- 您现在的位置:买卖IC网 > Sheet目录1999 > ICS932S890CKLF (IDT, Integrated Device Technology Inc)IC CLK CHIP EXPRESS 72MLF

932S890C

RD890 SYSTEM CLOCK FOR AMD-BASED SERVERS

IDT

RD890 SYSTEM CLOCK FOR AMD-BASED SERVERS

16

932S890C

REV D 052011

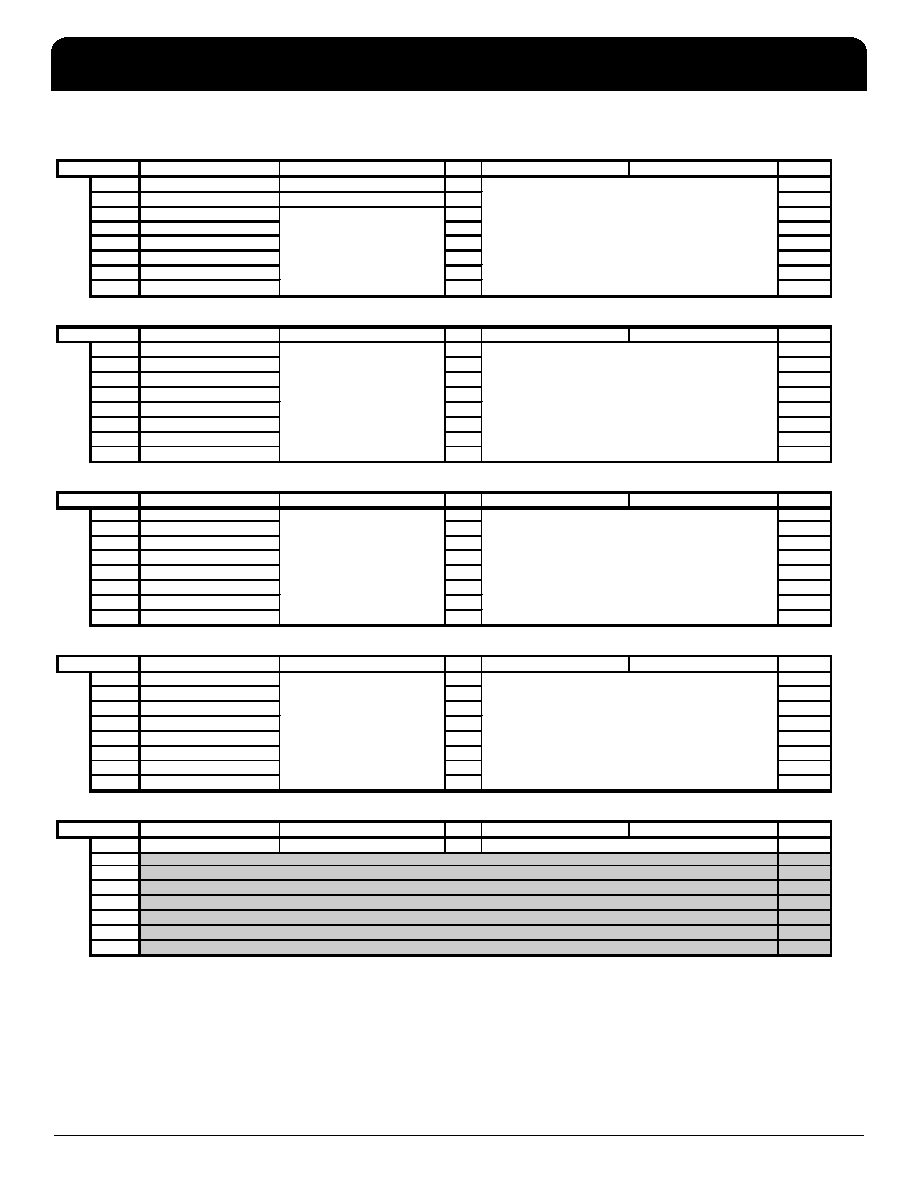

SMBUS Table: SR C Frequency Control Register

Byte

15

Name

Control Function

Type

0

1

Default

Bit 7

N Div2

N Divider Prog bit 2

R W

X

Bit 6

N Div1

N Divider Prog bit 1

R W

X

Bit 5

M Div5

R W

X

Bit 4

M Div4

R W

X

Bit 3

M Div3

R W

X

Bit 2

M Div2

R W

X

Bit 1

M Div1

R W

X

Bit 0

M Div0

R W

X

SMBUS Table: SR C Frequency Control Register

Byte

16

Name

Control Function

Type

0

1

Default

Bit 7

N Div10

R W

X

Bit 6

N Div9

RW

X

Bit 5

N Div8

RW

X

Bit 4

N Div7

RW

X

Bit 3

N Div6

RW

X

Bit 2

N Div5

RW

X

Bit 1

N Div4

RW

X

Bit 0

N Div3

RW

X

SMBUS Table: SR C Spread Spectrum Control Register

Byte

17

Name

Control Function

Type

0

1

Default

Bit 7

SSP7

R W

X

Bit 6

SSP6

R W

X

Bit 5

SSP5

R W

X

Bit 4

SSP4

R W

X

Bit 3

SSP3

R W

X

Bit 2

SSP2

R W

X

Bit 1

SSP1

R W

X

Bit 0

SSP0

R W

X

SMBUS Table: SR C Spread Spectrum Control Register

Byte

18

Name

Control Function

Type

0

1

Default

Bit 7

SSP15

R W

X

Bit 6

SSP14

R W

X

Bit 5

SSP13

R W

X

Bit 4

SSP12

R W

X

Bit 3

SSP11

R W

X

Bit 2

SSP10

R W

X

Bit 1

SSP9

R W

X

Bit 0

SSP8

R W

X

SMBus Table: SRC N Divider Control Register

Byte

19

Name

Control Function

Type

0

1

Default

Bit 7

SRC N Div0

LSB N Divider Programming

R W

X

Bit 6

0

Bit 5

0

Bit 4

0

Bit 3

0

Bit 2

0

Bit 1

0

Bit 0

0

Reserved

M Divider Programming

bit (5:0)

N Divider Programming

Byte16 bit(7:0) and Byte15

bit(7:6)

Reserved

N Divider LSB (bit 0) for SRC M/N programming.

The decimal representation of M and N Divider in Byte

15 and 16 configure the SRC VCO frequency. See

M/N Caculation Tables for VCO frequency formulas.

The decimal representation of M and N Divider in Byte

15 and 16 configure the SRC VCO frequency. See

M/N Caculation Tables for VCO frequency formulas.

Spread Spectrum

Programming bit(15:8)

Spread Spectrum

Programming bit(7:0)

These bits set the SRC spread pecentages.Please

contact IDT for the appropriate values.

These bits set the SRC spread pecentages.Please

contact IDT for the appropriate values.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ICS93716BGLF

IC DDR PLL CLOCK DRIVER 28-TSSOP

ICS94201DFLF

IC FREQ GENERATOR PROGR 56-SSOP

ICS950218AF

IC TIMING CTRL HUB P4 48-SSOP

ICS950908BFLF

IC TIMING CTRL HUB P4 56-SSOP

ICS951402AGLF

IC TIMING CTRL HUB P4 48-TSSOP

ICS95V847AGIT

IC CLOCK DRIVER 2.5V 24-TSSOP

ICS95V850AGT

IC CLK DVR PLL 1:10 48TSSOP

ICS95V857ALT

IC CLK DVR PLL 1:10 40TVSOP

相关代理商/技术参数

ICS932S890CKLFT

功能描述:IC CLK CHIP EXPRESS 72MLF RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS932SL901AKLF

制造商:Integrated Device Technology Inc 功能描述:IC ARM SERVER CLOCK 48MLF

ICS932SL901AKLFT

制造商:Integrated Device Technology Inc 功能描述:IC ARM SERVER CLOCK 48MLF

ICS932SQ420BGLF

功能描述:IC CLOCK SYNTHESIZER 64TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS932SQ420DGLF

功能描述:IC CLOCK SYNTHESIZER 64TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6

ICS932SQ420DGLFT

制造商:Integrated Device Technology Inc 功能描述:IDTICS932SQ420DGLFT ZERO DELAY FANOUT BU

ICS932SQ420DKLF

功能描述:IC CLOCK SYNTHESIZER 64QFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6

ICS932SQ420DKLFT

制造商:Integrated Device Technology Inc 功能描述:IC CLOCK SYNTHESIZER 64-QFP